# **EPROMs/PROMs/EEPROMs**

# 65.536-BIT UV ERASABLE PROGRAMMARIE READ-ONLY MEMORY

ন

GND

**PGM**

Vcc

Vpp

01-08

NC.

Output Enable

No Connection

5-V Power Supply

21-V Power Supply

Ground

Program

Outputs

|                                                                                           | JULY 1983 — REVISED MARCH 198                           |

|-------------------------------------------------------------------------------------------|---------------------------------------------------------|

| Organization 8192K × 8     Single 5-V Power Supply                                        | J PACKAGE<br>(TOP VIEW)                                 |

| Pin Compatible with Existing 64K EPROMs All Inputs and Outputs are TTL Compatible         | VPP 1 28 VCC<br>A12 2 27 PGM<br>A7 3 26 NC              |

| Max Access/Min Cycle Time     TMS2764-17                                                  | A6 4 25 A8 A5 5 24 A9 A4 6 23 A11 A3 7 22 G A2 B 21 A10 |

| <ul> <li>Low Standby Power Dissipation</li> <li>184 mW (Maximum)</li> </ul>               | A1 ☐ 9 20 ☐ Ē<br>A0 ☐ 10 19 ☐ Q8<br>Q1 ☐ 11 18 ☐ Q7     |

| JEDEC Approved Pinout     31 V Power Surely Possited for                                  | Q2                                                      |

| <ul> <li>21-V Power Supply Required for<br/>Programming</li> </ul>                        | GND <u>14 15</u> Q4                                     |

| <ul> <li>Fast Programming Algorithm</li> <li>N-Channel Silicon-Gate Technology</li> </ul> | PIN NOMENCLATURE  AO-A12 Address Inputs  E Chip Enable  |

# description

The TMS2764 is an ultraviolet-light erasable. electrically programmable read-only memory. It has 65,536 bits organized as 8,192 words of

PEP4 Version Available with 168 Hour

Temperature Range from -10°C to 85°C

**Burn-in and Guaranteed Operating**

(TMS2764-\_ JP4)

8-bit length. The TMS2764 only requires a single 5-volt power supply with a tolerance of ±5%.

The TMS2764 provides two output control lines: Output Enable (G) and Chip Enable (E). This feature allows the G control line to eliminate bus contention in microprocessor systems. The TMS2764 has a powerdown mode that reduces maximum power dissipation from 150 mA to 35 mA when the device is placed on standby.

This EPROM is supplied in a 28-pin, 15,2-mm (600-mil) dual-in-line ceramic package and is designed for operation from 0 °C to 70 °C. The TMS2764 is also offered in the PEP4 version with an extended guaranteed operating temperature range of -10°C to 85°C and 168 hour burn-in (TMS2764-\_\_JP4).

### operation

The six modes of operation for the TMS2764 are listed in the following table.

# TMS2764 65.536-BIT UV ERASABLE PROGRAMMABLE READ-ONLY MEMORY

| FUNCTION                         |      |                   |                         | MODE                |                         |                        |

|----------------------------------|------|-------------------|-------------------------|---------------------|-------------------------|------------------------|

| (PINS)                           | Read | Output<br>Disable | Power Down<br>(Standby) | Fast<br>Programming | Program<br>Verification | Inhibit<br>Programming |

| Ē<br>(20)                        | VIL  | χ <sup>†</sup>    | VIH                     | VIL                 | VIL                     | ViH                    |

| ট্ট<br>(22)                      | VIL  | VIH               | X <sup>†</sup>          | ∨ін                 | V <sub>IL</sub>         | χ <sup>†</sup>         |

| PGM<br>(27)                      | VIH  | VIH               | χ <sup>†</sup>          | VIL                 | VIH                     | χ†                     |

| V <sub>PP</sub> (1)              | vcc  | vcc               | vcc                     | Vpp                 | V <sub>PP</sub>         | VPP or VCC             |

| V <sub>CC</sub><br>(28)          | Vcc  | vcc               | vcc                     | vcc                 | vcc                     | Vcc                    |

| Q1-Q8<br>(11 to 13,<br>15 to 19) | DOUT | HI-Z              | HI-Z                    | D <sub>IN</sub>     | TUO <sup>Q</sup>        | HI-Z                   |

TX = VIH or VIL

### read/output disable

The two control pins ( $\overline{E}$  and  $\overline{G}$ ) must have low-level TTL signals in order to provide data at the outputs. Chip enable ( $\overline{E}$ ) should be used for device selection. Output enable ( $\overline{G}$ ) should be used to gate data to the output pins.

### power down

The power-down mode reduces the maximum active current from 150 mA to 35 mA. A TTL high-level signal applied to  $\overline{E}$  selects the power-down mode. In this mode, the outputs assume a high-impedance state, independent of  $\overline{G}$ .

### erasure

Before programming, the TMS2764 is erased by exposing the chip to shortwave ultraviolet light that has a wavelength of 253.7 nanometers (2537 angstroms). The recommended minimum exposure dose (UV intensity × exposure time) is fifteen watt-seconds per square centimeter. A typical 12 mW/cm² UV lamp will erase the device in approximately 20 minutes. The lamp should be located about 2.5 centimeters (1 inch) above the chip during erasure. After erasure, all bits are at a high level. It should be noted that normal ambient light contains the correct wavelength for erasure. Therefore, when using the TMS2764, the window should be covered with an opaque label.

### Fast programming

Note that the application of a voltage in excess of 22 V to Vpp may damage the TMS2764.

After erasure, logic Os are programmed into the desired locations. Programming consists of the following sequence of events. With the level on Vpp equal to 21 V and  $\overline{E}$  at TTL low, data to be programmed is applied in parallel to output pins Q1-Q8. The location to be programmed is addressed. Once data and addresses are stable, a TTL low-level pulse is applied to  $\overline{PGM}$ . Programming pulses must be applied at each location that is to be programmed. Locations may be programmed in any order.

# 1MS2/64 65.536-BIT UV ERASABLE PROGRAMMABLE READ-ONLY MEMORY

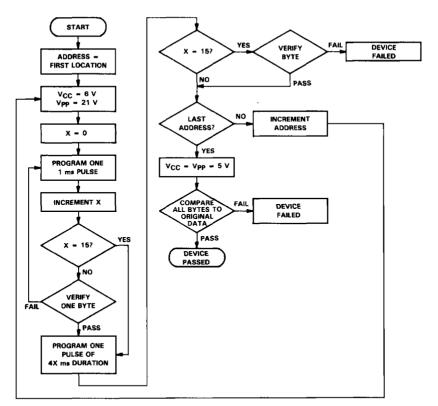

Programming uses two types of programming pulse: Prime and Final. The length of the Prime pulse is 1 millisecond; this pulse is applied X times. After each application, the byte being programmed is verified. If the correct data is read, the Final programming pulse is then applied. If correct data is not read, a further 1 millisecond programming pulse is applied up to a maximum X of 15. The Final programming pulse is 4X milliseconds long. This sequence of programming pulses and byte verification is done at  $V_{CC} = 6.0 \, \text{V}$  and  $V_{PP} = 21.0 \, \text{V}$ . When the full Fast programming routine is complete, all bits are verified with  $V_{CC} = V_{PP} = 5 \, \text{V}$ . A flowchart of the Fast programming routine is shown in Figure 1.

### multiple device programming

Several TMS2764s can be programmed simultaneously by connecting them in parallel and following the programming sequence previously described.

### program inhibit

The program inhibit is useful when programming multiple TMS2764s connected in parallel with different data. Program inhibit can be implemented by applying a high-level signal to  $\overline{E}$  or  $\overline{PGM}$  of the device that is not to be programmed.

### program verify

Programmed bits may be verified with Vpp = 21 V when  $\overline{G} = V_{IL}$ ,  $\overline{E} = V_{IL}$  and  $\overline{PGM} = V_{IH}$ .

FIGURE 1. FAST PROGRAMMING FLOWCHART

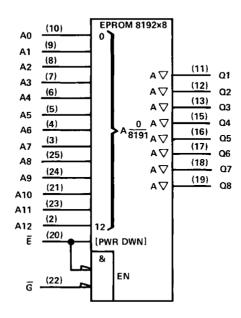

# logic symbol†

<sup>&</sup>lt;sup>†</sup>This symbol is in accordance with ANSI/IEEE Std. 91-1984 and IEC Publication 617-12.

# absolute maximum ratings over operating free-air temperature range (unless otherwise noted)‡

| Supply voltage range, VCC            | -0.6 V to 7 V  |

|--------------------------------------|----------------|

| Supply voltage range, Vpp            | -0.6 V to 22 V |

| Input voltage range                  | -0.6 V to 7 V  |

| Output voltage range                 | -0.6 V to 7 V  |

| Operating free-air temperature range | 0°C to 70°C    |

| Storage temperature range            | -65°C to 150°C |

<sup>&</sup>lt;sup>‡</sup> Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the "Recommended Operating Conditions" section of this specification is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

# recommended operating conditions

|     |                                      | MIN  | NOM | MAX                | UNIT |

|-----|--------------------------------------|------|-----|--------------------|------|

| Vcc | Supply voltage                       | 4.75 | 5   | 5.25               | ٧    |

| VPP | Supply voltage                       |      | Vcc |                    |      |

| VIH | High-level input voltage             | 2    |     | V <sub>CC</sub> +1 | ٧    |

| VIL | Low-level input voltage (see Note 1) | -0.1 |     | 8.0                | >    |

| TA  | Operating free-air temperature       | 0    |     | 70                 | °C   |

NOTE 1: The algebraic convention, where the more negative (less positive) limit is designated as minimum is used in this data sheet for logic voltage levels only.

# TMS2764 65.536-BIT UV ERASABLE PROGRAMMABLE READ-ONLY MEMORY

# electrical characteristics over full ranges of recommended operating conditions

|      | PARAMETER                                | TEST CONDITIONS                  | MIN M | AX | UNIT |

|------|------------------------------------------|----------------------------------|-------|----|------|

| Voн  | High-level output voltage                | I <sub>OH</sub> = -400 μA        | 2.4   |    | ٧    |

| VOL  | Low-level output voltage                 | I <sub>OL</sub> = 2.1 mA         | 0.    | 45 | V    |

| 1    | Input current (load)                     | V <sub>I</sub> = 0 V to 5.25 V   | ±     | 10 | μA   |

| ю    | Output current (leakage)                 | V <sub>O</sub> = 0.4 V to 5.25 V | ±     | 10 | μΑ   |

| lPP1 | Vpp supply current (read)                | Vpp 5.25 V                       |       | 15 | mΑ   |

| IPP2 | Vpp supply current (program)             | E and PGM at V <sub>IL</sub>     |       | 50 | mA   |

| lCC1 | V <sub>CC</sub> supply current (standby) | E at VIH                         |       | 35 | mA   |

| lcc2 | V <sub>CC</sub> supply current (active)  | Ē and Ō at V <sub>II.</sub>      | 1     | 50 | mA   |

# capacitance over recommended supply voltage range and operating free-air temperature range, $f = 1 \text{ MHz}^{\dagger}$

|    | PARAMETER          | TEST CONDITIONS      | TYP‡ | MAX | UNIT |

|----|--------------------|----------------------|------|-----|------|

| Ci | Input capacitance  | V <sub>I</sub> = 0 V | 6    | 9   | рF   |

| Co | Output capacitance | V <sub>O</sub> = 0 V | 8    | 12  | pF   |

<sup>&</sup>lt;sup>†</sup>Capacitance measurements are made on a sample basis only.

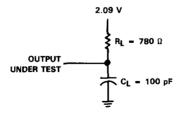

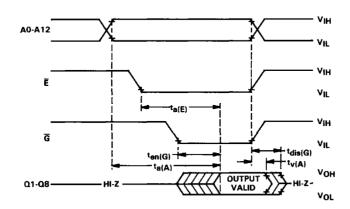

# switching characteristics over recommended supply voltage range and operating free-air temperature range, C<sub>L</sub> = 100 pF, 1 Series 74 TTL load (see Note 2 and Figure 2)

|                    | DADAMETED                                                                       | TMS2764-17 |     | TMS2764-20 |         | TMS2764-25 |         | TMS2764-45 |      |    |

|--------------------|---------------------------------------------------------------------------------|------------|-----|------------|---------|------------|---------|------------|------|----|

| PARAMETER          |                                                                                 | MIN MAX    |     | MIN MAX    | MIN MAX |            | MIN MAX |            | UNIT |    |

| ta(A)              | Access time from address                                                        |            | 170 |            | 200     |            | 250     |            | 450  | ns |

| t <sub>a(E)</sub>  | Access time from E                                                              |            | 170 |            | 200     |            | 250     |            | 450  | ns |

| ten(G)             | Output enable time from G                                                       |            | 65  |            | 75      |            | 100     |            | 150  | ns |

| tdis(G)§           | Output disable time from G                                                      | 0          | 60  | 0          | 60      | ٥          | 85      | 0          | 130  | ns |

| t <sub>V</sub> (A) | Output data valid time after change of address, E, or G, whichever occurs first | 0          |     | 0          |         | 0          |         | 0          |      | ns |

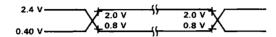

NOTE 2: For all switching characteristics and timing measurements, input pulse levels are 0.40 V and 2.4 V. Input and output timing reference levels are 0.8 V and 2.0 V.

<sup>&</sup>lt;sup>‡</sup>Typical values are at T<sub>A</sub> = 25°C and nominal voltage.

<sup>&</sup>lt;sup>§</sup>Value calculated from 0.5 V delta to measured output level; t<sub>dis(G)</sub> is specified from  $\overline{G}$  or  $\overline{E}$ , whichever occurs first. Refer to read-cycle timing diagram. This parameter is only sampled and not 100% tested.

# 6

# TMS2764 65.536-BIT UV ERASABLE PROGRAMMABLE READ-ONLY MEMORY

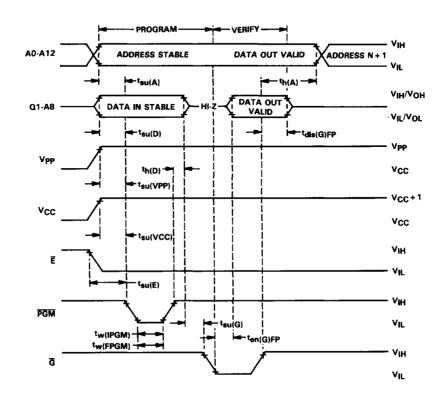

recommended conditions for Fast programming routine,  $T_A = 25$  °C (see Note 2 and Fast programming cycle time diagram)

|                      | PARAMETER                                       | MIN  | NOM | MAX  | UNIT |

|----------------------|-------------------------------------------------|------|-----|------|------|

| VCC                  | Supply voltage (see Note 3)                     | 5.75 | 6   | 6.25 | V    |

| V <sub>PP</sub>      | Supply voltage (see Note 4)                     | 20.5 | 21  | 21.5 | ٧    |

| tw(IPGM)             | PGM initial program pulse duration (see Note 5) | 0.95 | 1   | 1.05 | ms   |

| tw(FPGM)             | PGM final pulse duration (see Note 6)           | 3.8  |     | 63   | ms   |

| t <sub>su(A)</sub>   | Address setup time                              | 2    |     |      | μS   |

| t <sub>su(D)</sub>   | Data setup time                                 | 2    |     |      | μs   |

| t <sub>su(VPP)</sub> | Vpp setup time                                  | 2    |     |      | μS   |

| t <sub>su(VCC)</sub> | V <sub>CC</sub> setup time                      | 2    |     |      | μS   |

| th(A)                | Address hold time                               | 0    |     |      | μS   |

| <sup>t</sup> h(D)    | Data hold time                                  | 2    |     |      | μS   |

| t <sub>su(E)</sub>   | E setup time                                    | 2    |     |      | μs   |

| t <sub>sulG</sub> }  | G setup time                                    | 2    |     |      | μS   |

# Fast programming characteristics, TA = 25 °C (see Note 2 and Fast programming cycle timing diagram)

|           | PARAMETER                                              | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|-----------|--------------------------------------------------------|-------------------------|-----|-----|-----|------|

| tdis(G)FP | Output disable time from \$\overline{G}\$ (see Note 7) | C <sub>L</sub> = 100 pF | 0   |     | 130 | ns   |

| ten(G)FP  | Output enable time from G                              | 1 Series 74 TTL Load    |     |     | 150 | 115  |

NOTES: 2. For all switching characteristics and timing measurements, input pulse levels are 0.40 V and 2.4 V. Input and output timing reference levels are 0.8 V and 2.0 V.

- 3. VCC must be applied simultaneously or before Vpp and removed simultaneously or after Vpp.

- When programming the TMS2764, connect a 0.1 μF capacitor between Vpp and GND to suppress spurious voltage transients which may damage the device.

- 5. The Initial program pulse duration tolerance is 1 ms ±5%.

- 6. The length of the Final pulse will vary from 3.8 ms to 63 ms depending on the number of Initial pulse applications (X).

- 7. This parameter is only sampled and is not 100% tested.

# PARAMETER MEASUREMENT INFORMATION

NOTE 8:  $t_f \le 20 \text{ ns}$  and  $t_r \le 20 \text{ ns}$ .

# FIGURE 2. TYPICAL OUTPUT LOAD CIRCUIT

# AC testing input/output wave forms

A.C. testing inputs are driven at 2.4 for logic 1 and 0.4 V for logic 0. Timing measurements are made at 2.0 V for logic 1 and 0.8 V for logic 0 for both inputs and outputs.

# read cycle timing

# fast program cycle timing